|

I'm currently an engineer at SiFive where I continue to maintain FireSim. I received my Ph.D. in Electrical Engineering and Computer Science in May 2021 from the University of California, Berkeley. There I was part of the Berkeley Architecture Research (BAR) Group and co-advised by Jonathan Bachrach and Krste Asanović. My dissertation, titled Automated, FPGA-Based Hardware Emulation of Dynamic Frequency Scaling, explores techniques for simulating ASIC clock switching and generation structures using commerical off-the-shelf FPGAs. I received my BASc. in Engineering Science in the Electrical and Computer Engineering Option at the University of Toronto in 2015 (1T3 + PEY). |

|

|

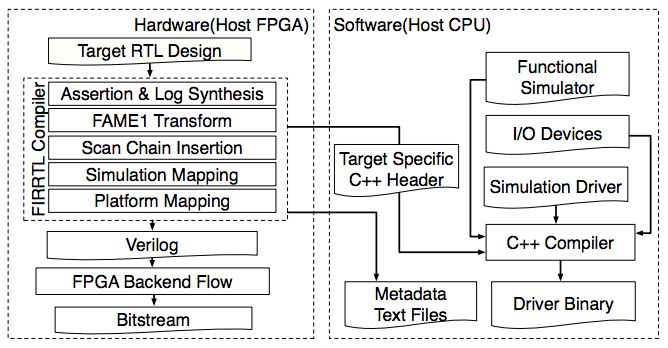

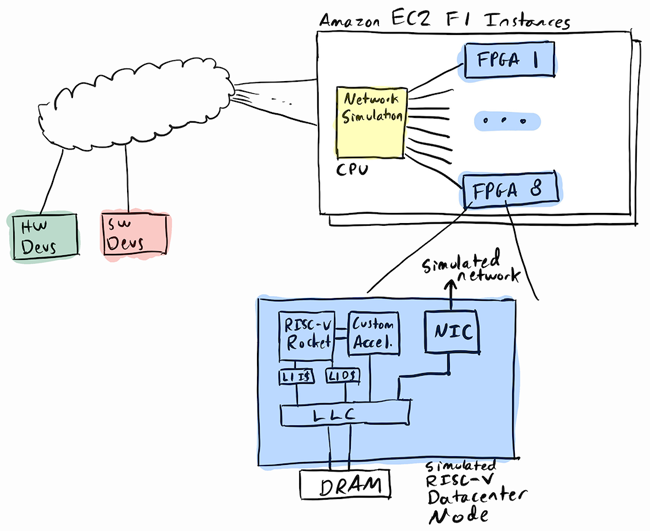

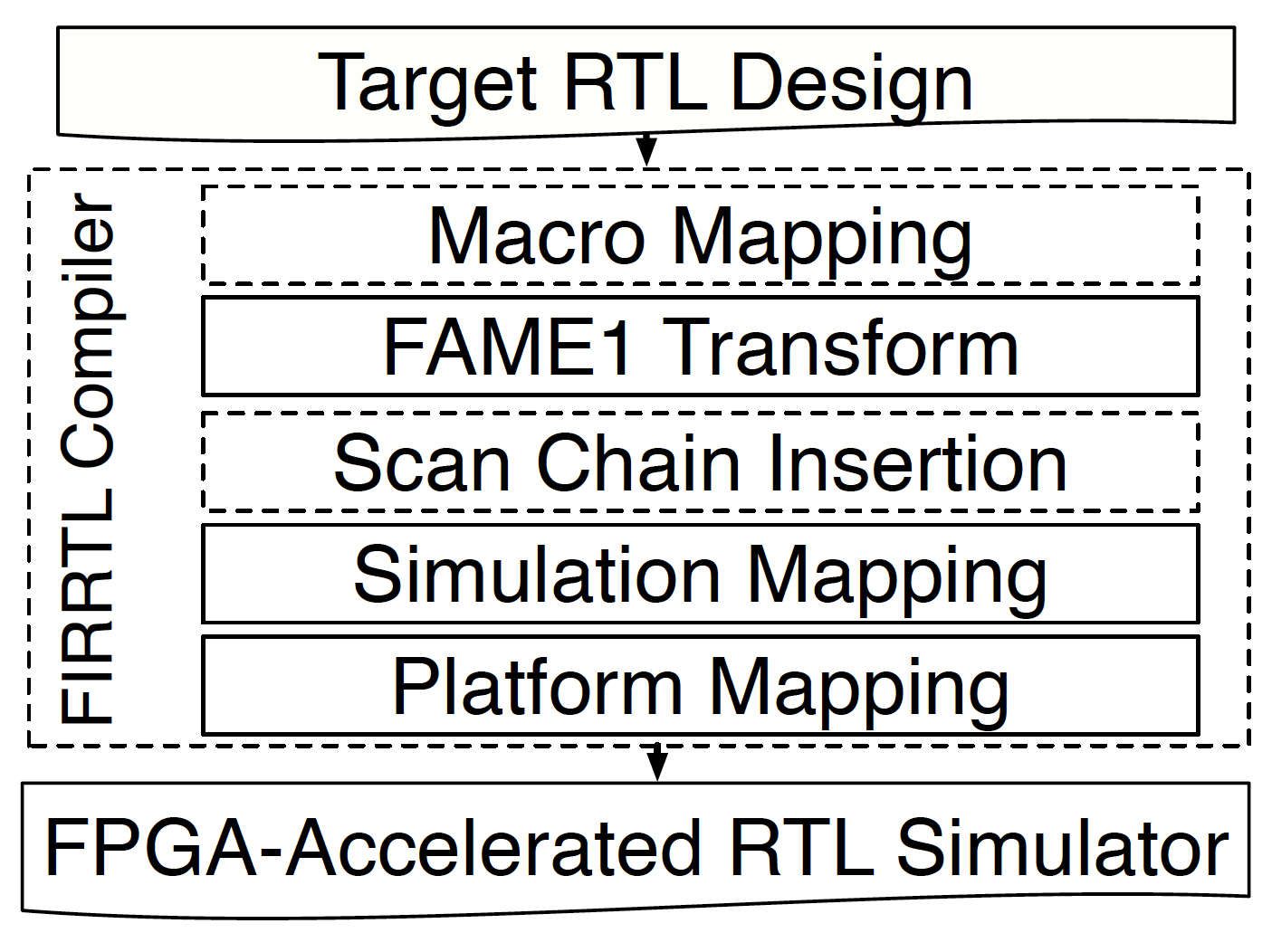

I'm interested in all things related to the design of VLSI systems, from transistors to CAD. With the end of Moore's law in sight, advances in computing performance and energy effiency must increasingly come from innovations above the process technology. In an effort to make hardware design more accessible, my research studies new FPGA-accelerated simulation (colloquially, hardware emulation) to help designers verify and validate their systems easily using relatively inexpensive FPGAs-in-the-cloud (AWS EC2 F1). I'm a maintainer of the FireSim project, which builds FPGA-based hardware emulators of RISCV-based systems spanning single SoCs to warehouse-scale computers. My work focusses on the hardware compiler at the heart of FireSim, called Golden Gate (MIDAS II). Golden Gate generates bit- and cycle-exact models from ASIC RTL, and provides additional tooling to support deterministic software co-simulation of parts of the simulator where an FPGA-hosted model is not required. |

|

|

|

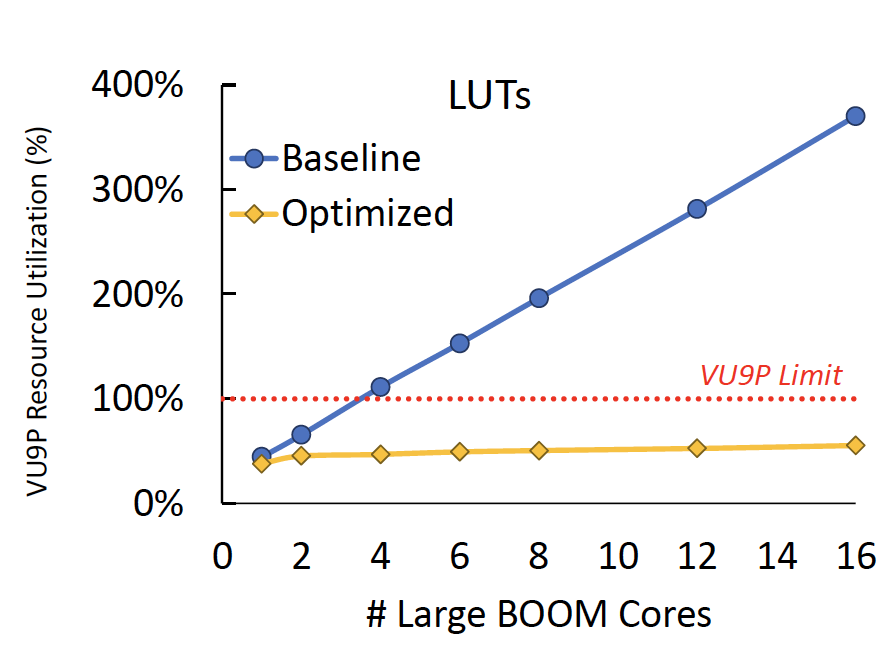

Here we explore two developments in FireSim: support for multi-clock target systems and more advanced resource optimizations. Of particular note is instance multithreading which can enable up to an 8x increase in single FPGA capacity. This publication serves as teaser for Albert Magyar's and my own dissertation work. |

|

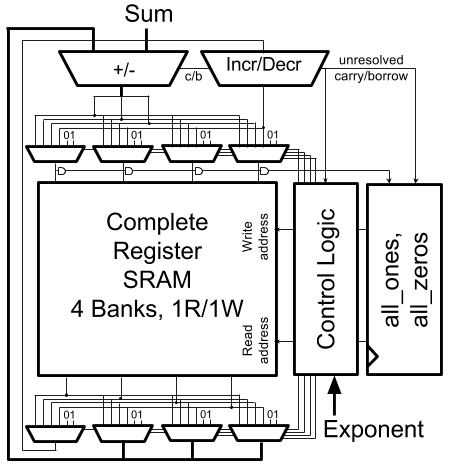

We present Golden Gate (MIDAS II): the first optimizing FPGA-accelerated simulator compiler. By replacing multi-ported register files with a BRAM-based model, Golden Gate enabled us to fit six cores on an FPGA that could only fit four previously. We also present LIME, a bounded model-checking flow to verify that the optimized simulator is faithful to the source RTL. |

|

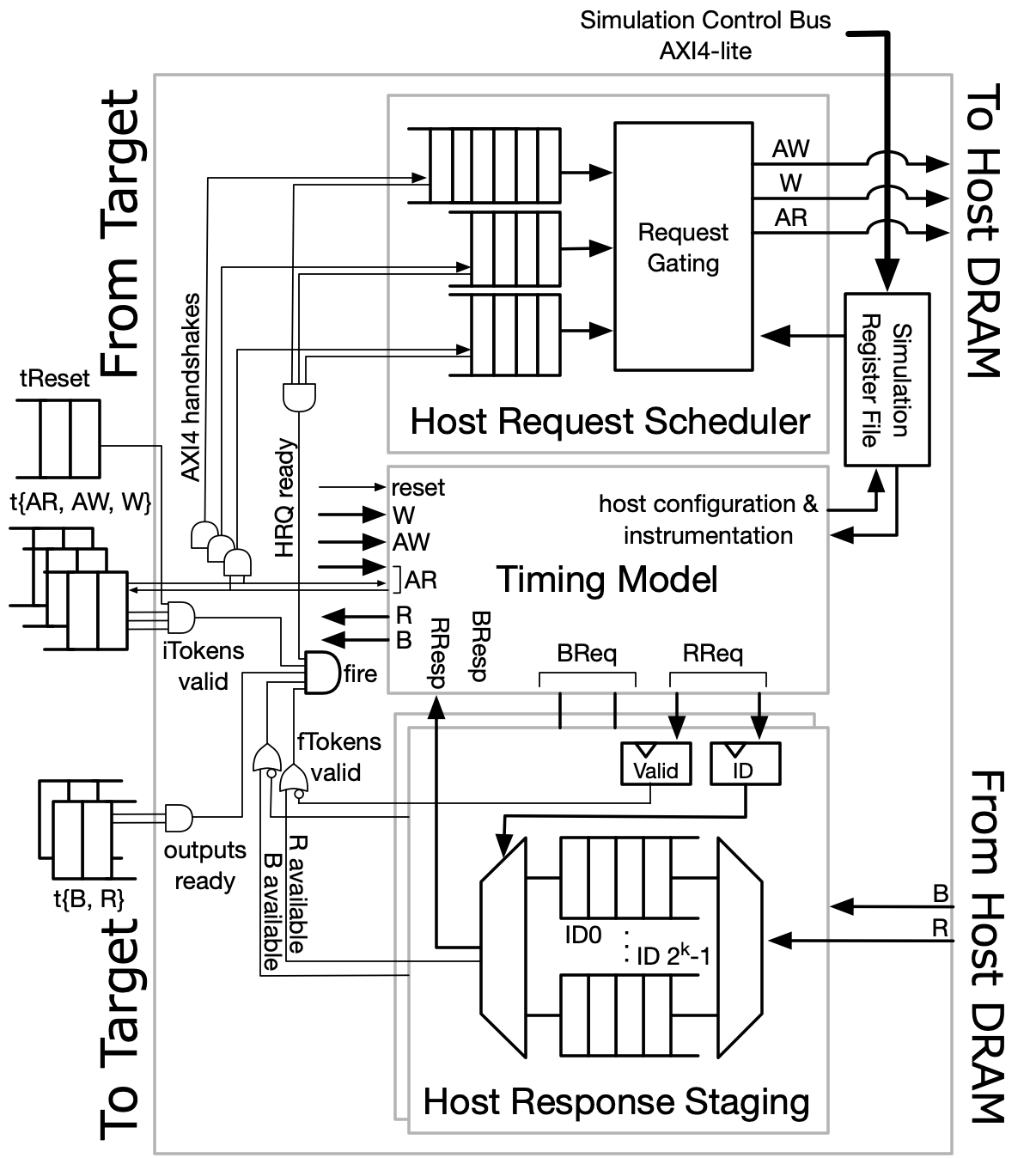

In this paper we present FASED, the generator of high-fidelity, reconfigurable, FPGA-hosted, last-level-cache and DRAM timing models used in FireSim. |

|

Augmenting MIDAS, DESSERT introduces two mechanisms for bug detection: assertion synthesis and online golden-model checking. Using a techinque we call ganged simulation, DESSERT runs two simulations in parallel, one running ahead of the other, to capture a full-visibility waveform of the design before the bug manifests without simulation slowdown. |

|

FireSim is a cycle-exact, FPGA-accelerated, scale-out computer system simulation platform. The FPGA-hosted components of a FireSim simulator are generated using MIDAS, which transforms Rocket Chip-generated RTL to produce the nodes of the system. |

|

The first public demonstration of MIDAS. MIDAS builds on the work of Strober: it has been ported to Chisel3 and FIRRTL, and produces FPGA-accelerated simulators that are tenfold faster. With the improved speed, we collect energy and performance results from both BOOM and rocket-based processors generated by the Rocket Chip SoC Generator, as they run the SPEC2006int benchmark with reference inputs to completion. |

|

We study the implementation of a hardware accelerator, designed in Chisel and hosted in a Rocket Chip-generated SoC, that computes a dot product of IEEE-754 floating-point numbers exactly. The accelerator uses a wide (640 or 4288 bits for single or double-precision respectively) fixed-point representation into which intermediate floating-point products are accumulated. |

|

Here we present an update of our GENIE paper originally presented at FPGA2015. |

|

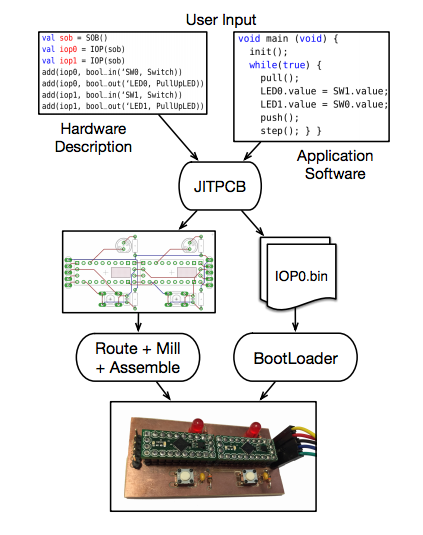

Commercialization of desktop milling machines has made rapid Printed Circuit Board (PCB) fabrication accessible. Unfortunately, PCB design for embedded and robotic systems is still a tedious and time consuming activity. In this paper, we present a technique, Just In Time Printed Circuit Board (JITPCB) for designing PCB systems at speeds commensurate with the capability of desktop PCB milling machines. |

|

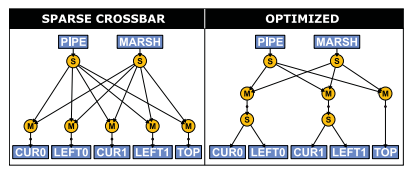

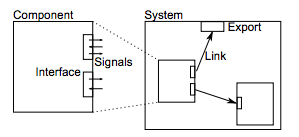

We present GENIE, a tool to generate optimized FPGA interconnect at

finer granularity of design—just above the pipeline level—than

commercial system integration tools like Altera's QSYS. |

|

|

|

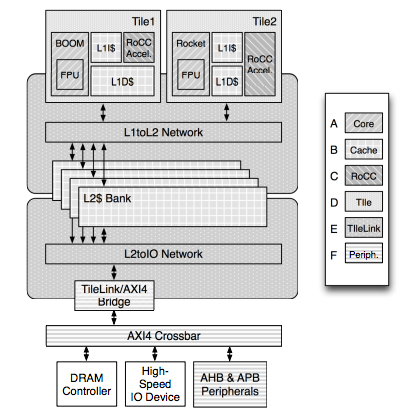

Rocket Chip is an open-source System-on-Chip(SoC) design generator that emits synthesizable RTL. It leverages the Chisel hardware construction language to compose a library of sophisticated generators for cores, caches, and interconnects into an integrated SoC. |

|

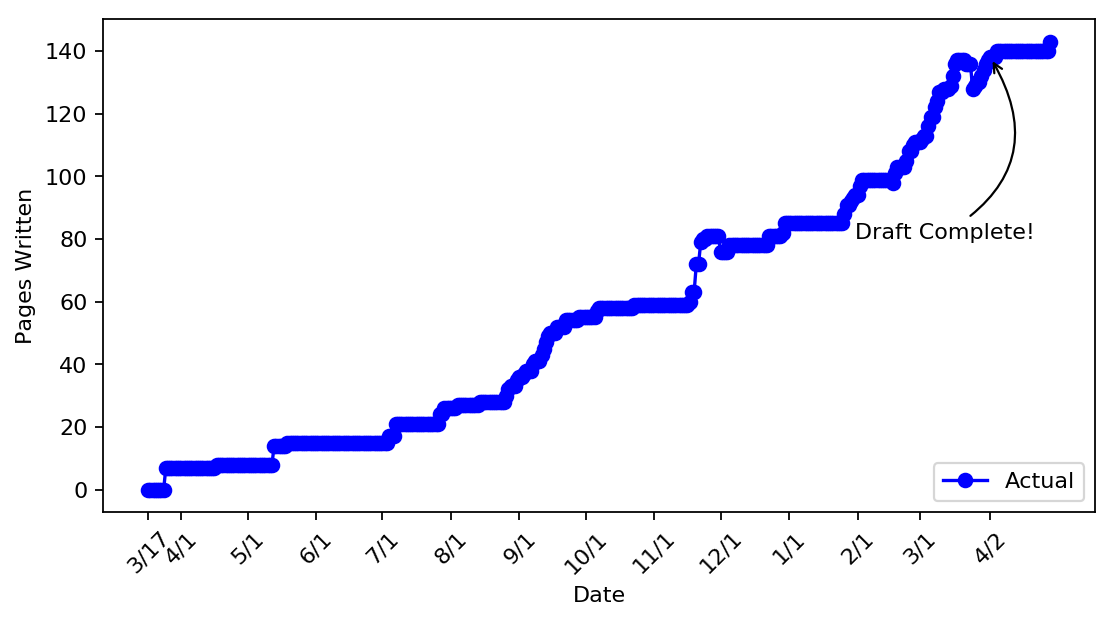

My dissertation work studied mechanisms for simulating digital systems with multiple dynamically scaling clocks using commercial-off-the-shelf FPGA platforms. I've preserved my page-count progress from March 2020 to April 2021 here for posterity. [Scripts courtesy Andrew Waterman]

|

|

|

In my free time I like to climb, hike, and ski. I love to ride bikes, both on the road and on the trail. I used to race XC mountain bikes with the University of Toronto Blues and the Lapdogs Cycling Club. When not outdoors, I enjoy cooking for people and learning new (natural) languages. I maintain this Anki Deck for Berkeley J1A and J1B students. |

|

|